SDI出力「59.94Hz」に対応するために、フレームレート周波数を調整する方法とは?

(この記事の所要時間は約3分です)

ビデオ通信速度を決定する為のクロック周波数は、 デバイス間との通信や内部制御する周波数のズレにより、さまざまな問題が発生します。

特にお客様からお問い合わせ頂くのは、「セキュリティ用途:60Hzを、Broadcast用途59.94Hzへ流用する際に、フレームレート周波数の調整ができない」というものです。そこで今回はこの要因と、解決方法についてご紹介します。

問題事例

1920x1080i59.94(SDI出力)を出力するためにPixel-Clock:74.175MHz設定。しかし、ビデオ信号のジッタや周波数安定度が開発会社の自社規格外の値になってしまった。

考えられる要因

1.使用条件の変化

まず、環境による変化が要因としてあげられます。温度・湿度・気圧、使用環境は周波数のズレをおこす要因の1つです。

2.基板パターン設計上

基板パターン上に、複数の周波数が混在する場合、

・ノイズ

・ジッタ発生、または増加

この2つがクロックや同期信号に影響を及ぼしている可能性があります。

3.クロック/フレーム生成のメカニズム

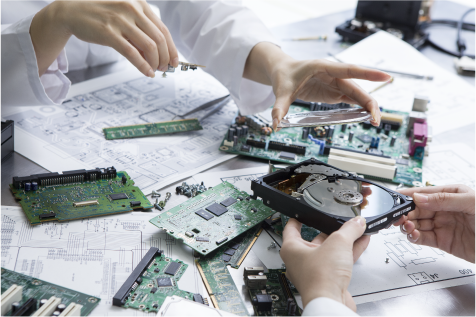

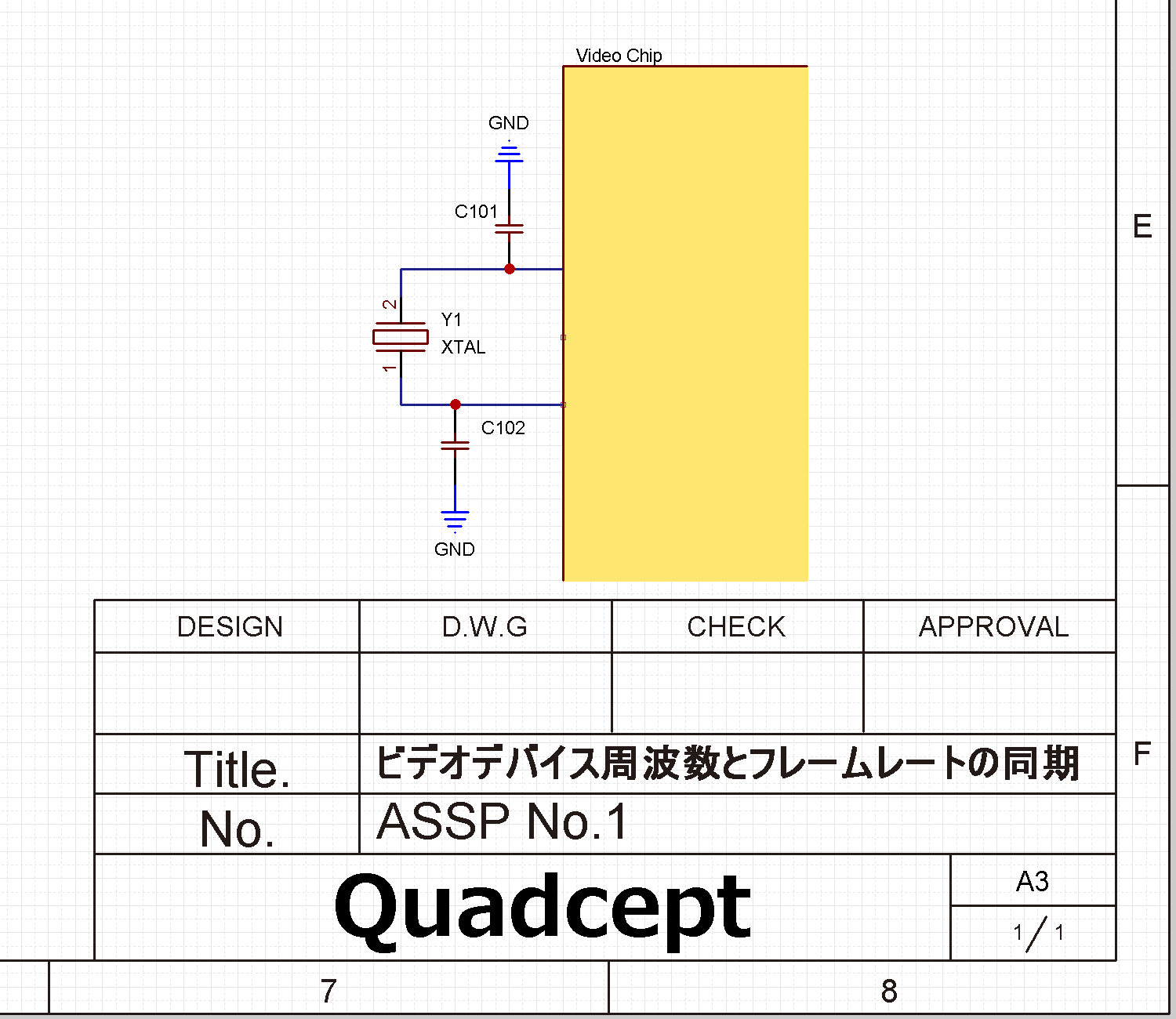

入力非同期の場合、ビデオデバイスの出力周波数は、下図のようにリファレンスとなる源信クロック Xtal/Xtal Osillator(水晶発振器)をもとにして、内部PLLで同期がされます。

出力側の同期 ブロック図

このため、フレームレート29.97Hz / 59.94Hzなどの周波数を詳細設定時には、調整が必要となります。周波数精度が開発製品規格の基準値に達成しないため、こういった状況がおきるのです。

ADT技術サポートからの提案

改善案1:PLL (Phase Locked Loop)設定値の見直し

59.9HzのPLL周波数設定時は、各メーカー推奨の基本設定値が採用されていますが、これが外部要因や入力ビデオの問題PLLのクセなども関係しているかもしれません。このような場合、PLL設定値の見直しと出力画像特性を把握することで解決に結びつく可能性があります。例えば、「Macro Image Technology」では、以下のような設定変更することで改善しました。

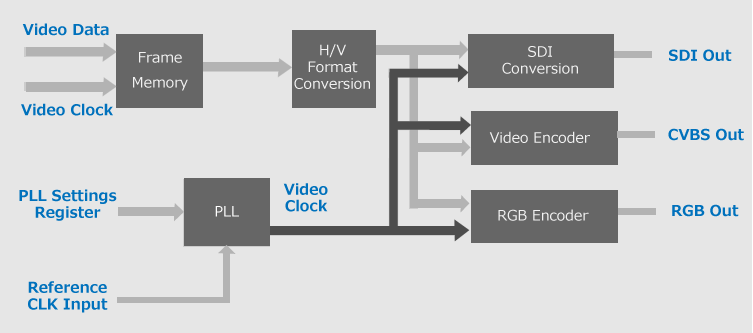

Figure 3-28. Structure of Internal PLL

上図はMacro Image Technology MDIN-380 内蔵PLL構成です。Pixel周波数はPost Divider(M) 、Pre Divider(P)、Post Scaler( S)を設定しますが、デフォルト値M, P, Sは [250, 91, 1]でした。そこで同期周波数などを見直し、 M, P, Sを[250, 13, 7]へ変更したところ、ジッタの改善と周波数が安定しました。

改善案2:クロックリファレンス用 発信器の周波数調整

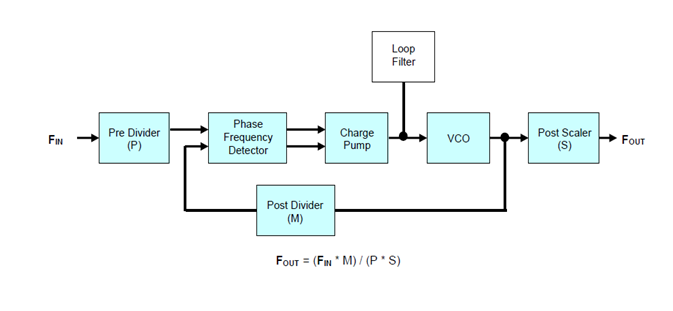

以下はリファレンス周波数の入力部の回路です。

発振を安定にさせるためには、下記回路図の様に両端にコンデンサを付加する必要があます。当社総代理店「Macro Image Technology」製品では、Y1=27MHzにおいてC101/C102=18pF を推奨ていますが、基板上に搭載されるデバイスが異ったり、パタンの引き回しの違いにより必ずしもこの値が正解とは限りません。実際に、周波数安定度が悪かった基板にて、これらC101/C102を数pF変更した事により周波数安定度を改善することができました。

*作成回路図(Quadcept)

改善案3:出力ビデオClockの源信(素材)を変更

回路構成時、外部発信器+PLLでは求める周波数精度が得られないケースがありました。その回路では、入力ビデオ信号のクロックがBroadcast仕様を満たしています、これ使用すればで周波数安定度が向上する可能性があるのではないかと考えました。

以上のことからPLL入力のリファレンスを外部発信器からビデオ入力クロックへ切替えた結果、内蔵PLLで付加されるジッタを現象させることができ、クロック周波数の安定度が向上しました。

総括

上記に紹介した記事は、実際に問題となったビデオ処理に関する事例です。

クロックやフレームの周波数安定度に関するトラブルにおいて、意外に見落としがちなこれらの基本的な要因を、今一度、再確認してみては如何でしょうか。